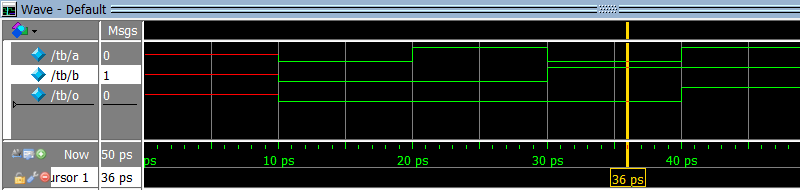

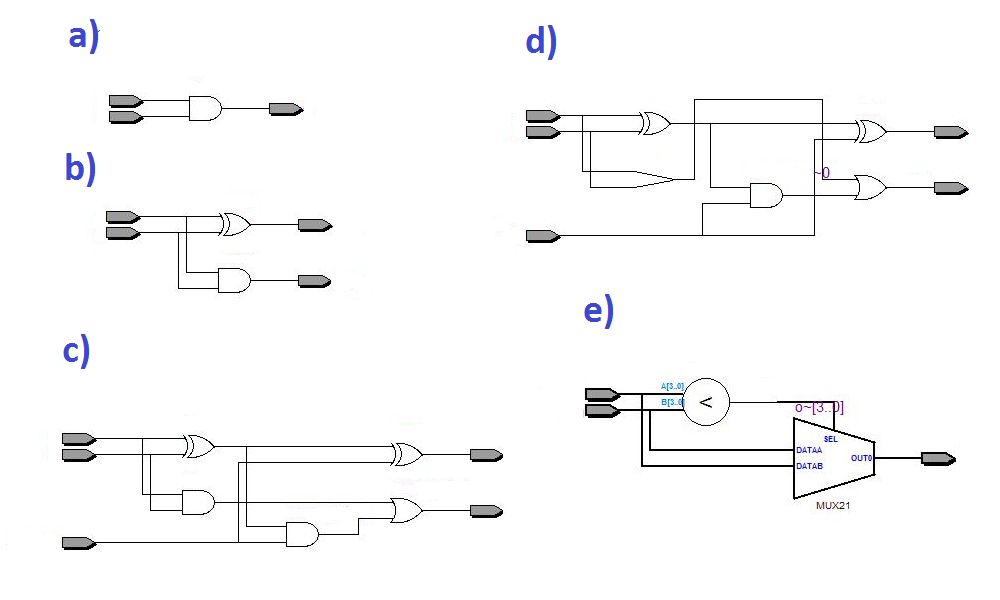

b)

b)

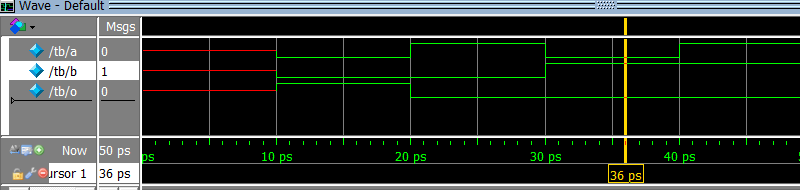

c)

c)

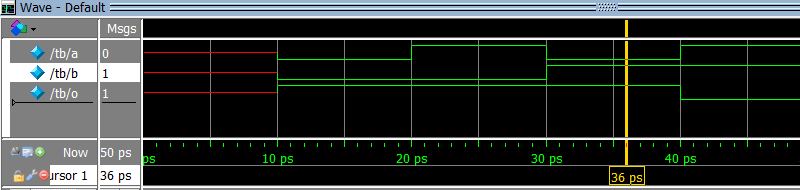

d)

d)

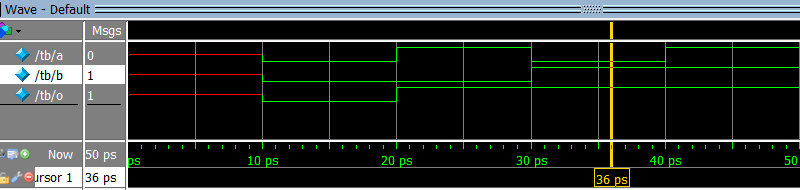

e)

e)

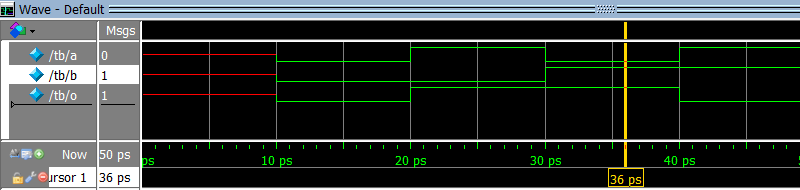

2. What is the result of synthesis of this module?

module design

(

input [3:0] a,

input [3:0] b,

output [3:0] o

);

assign o = a < b ? a : b;

endmodule

2. What is the result of synthesis of this module?

module design

(

input [3:0] a,

input [3:0] b,

output [3:0] o

);

assign o = a < b ? a : b;

endmodule

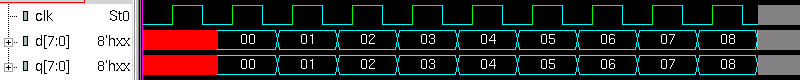

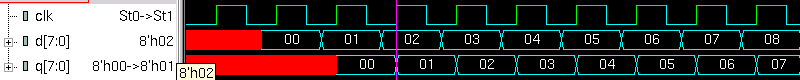

3. Which waveform is the simulation result of Verilog code below?

module dut

(

input clk,

input [7:0] d,

output logic [7:0] q

);

logic [7:0] r;

always @(posedge clk)

begin

r = d;

q <= r;

end

endmodule

module testbench;

logic clk;

logic [7:0] d, q;

dut dut (clk, d, q);

initial

begin

clk = 0;

forever

end

initial

begin

$dumpvars ();

for (int i = 0; i < 10; i++)

begin

@(posedge clk);

d = i;

end

$finish;

end

endmodule

a)

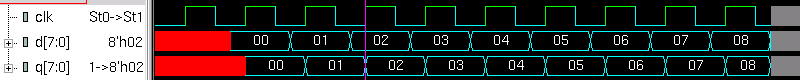

3. Which waveform is the simulation result of Verilog code below?

module dut

(

input clk,

input [7:0] d,

output logic [7:0] q

);

logic [7:0] r;

always @(posedge clk)

begin

r = d;

q <= r;

end

endmodule

module testbench;

logic clk;

logic [7:0] d, q;

dut dut (clk, d, q);

initial

begin

clk = 0;

forever

end

initial

begin

$dumpvars ();

for (int i = 0; i < 10; i++)

begin

@(posedge clk);

d = i;

end

$finish;

end

endmodule

a)

b)

b)

c)

c)

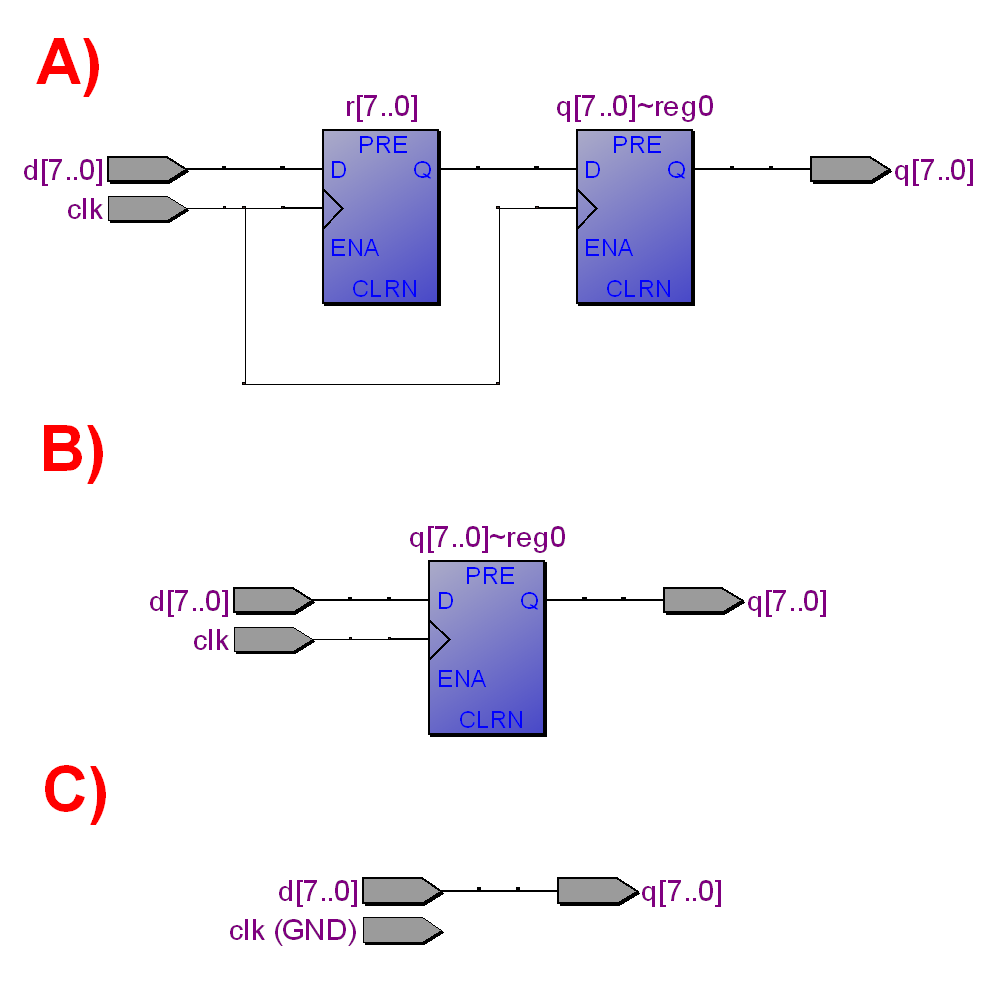

4. What schematics correspond to Verilog code below?

module dut

(

input clk,

input [7:0] d,

output logic [7:0] q

);

logic [7:0] r;

always @(posedge clk)

begin

r = d;

q <= r;

end

endmodule

4. What schematics correspond to Verilog code below?

module dut

(

input clk,

input [7:0] d,

output logic [7:0] q

);

logic [7:0] r;

always @(posedge clk)

begin

r = d;

q <= r;

end

endmodule

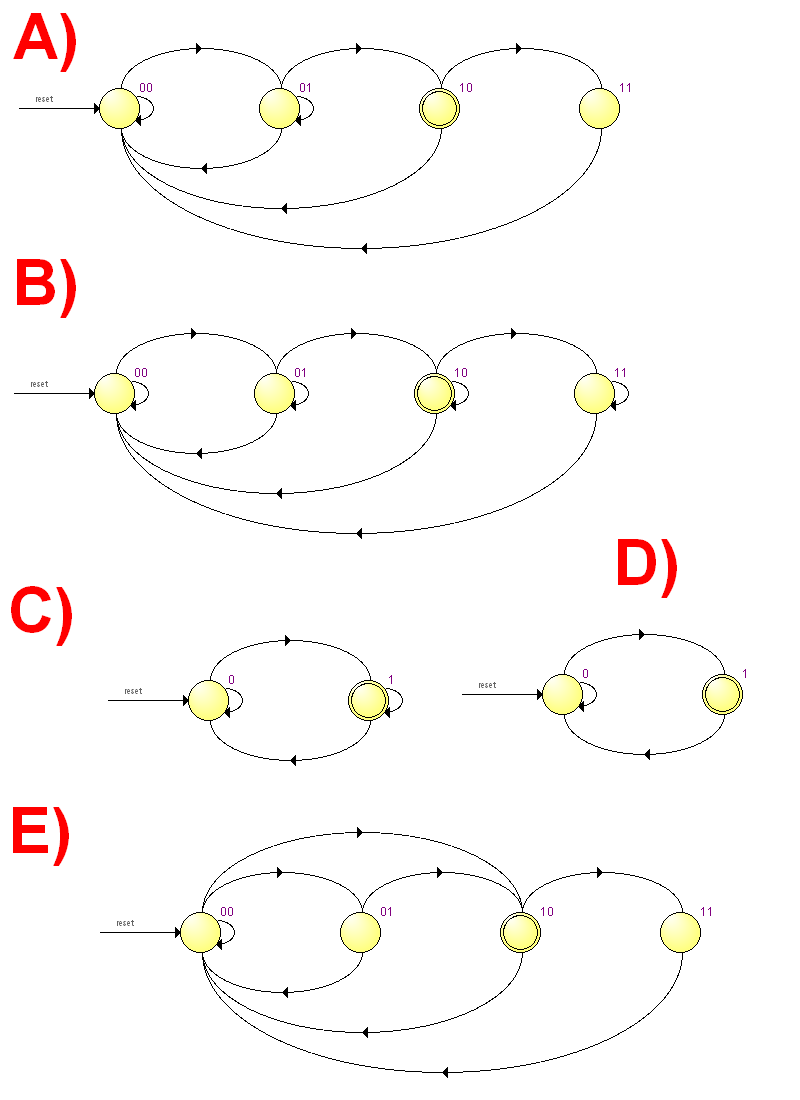

5. What Finite State Machine (FSM) state diagram correspond to Verilog code below?

module dut

(

input clk,

input resetn,

input a,

output b

);

logic [0:0] state;

always @(posedge clk)

if (! resetn)

state <= 0;

else

case (state)

0: state <= 1;

1: state <= 0;

endcase

assign b = (state == 1);

endmodule

5. What Finite State Machine (FSM) state diagram correspond to Verilog code below?

module dut

(

input clk,

input resetn,

input a,

output b

);

logic [0:0] state;

always @(posedge clk)

if (! resetn)

state <= 0;

else

case (state)

0: state <= 1;

1: state <= 0;

endcase

assign b = (state == 1);

endmodule

The code below contains three modules implementing the same functionality, calculating the power of five of a given number. Analyze the code and answer the following questions: module pow_5_implementation_1 ( input clock, input reset_n, input run, input [17:0] n, output ready, output [17:0] n_pow_5 ); reg [4:0] shift; always @(posedge clock or negedge reset_n) if (! reset_n) shift <= 0; else if (run) shift <= 5'b10000; else shift <= shift >> 1; assign ready = shift [0]; reg [17:0] r_n, mul; always @(posedge clock) if (run) begin r_n <= n; mul <= n; end else begin mul <= mul * r_n; end assign n_pow_5 = mul; endmodule //-------------------------------------------------------------------- module pow_5_implementation_2 ( input clock, input [17:0] n, output reg [17:0] n_pow_5 ); reg [17:0] n_1, n_2, n_3; reg [17:0] n_pow_2, n_pow_3, n_pow_4; always @(posedge clock) begin n_1 <= n; n_2 <= n_1; n_3 <= n_2; n_pow_2 <= n * n; n_pow_3 <= n_pow_2 * n_1; n_pow_4 <= n_pow_3 * n_2; n_pow_5 <= n_pow_4 * n_3; end endmodule //-------------------------------------------------------------------- module pow_5_implementation_3 ( input [17:0] n, output [17:0] n_pow_5 ); assign n_pow_5 = n * n * n * n * n; endmodule

6. Which implementation is purely combinational? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

7. Which implementation is sequential? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

8. Which implementation is pipelined? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

9. Identify the implementation that corresponds to the following schematics: a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

10. Identify the implementation that corresponds to the following schematics: a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

11. Identify the implementation that corresponds to the following schematics: a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3 d) pow_5_implementation_1 and pow_5_implementation_2 e) pow_5_implementation_1 and pow_5_implementation_3 f) pow_5_implementation_2 and pow_5_implementation_3 g) all of them h) none of them

12. Which implementation is likely to allow the highest maximum frequency (assuming that the outputs of the combinational implementation are connected to clocked register)? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3

13. Which implementation is likely to use the smallest number of gates? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3

14. Which implementation is likely to have the highest throughput (number of calculated pow_5(n) results per seconds)? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3

15. Which implementation is going to have the smallest latency in clock cycles (assuming that the outputs of the combinational implementation are connected to clocked registers)? a) pow_5_implementation_1 b) pow_5_implementation_2 c) pow_5_implementation_3

16. The testbench instantiated all three implementations of pow_5. module testbench; reg clock; reg reset_n; reg run; reg [17:0] n; wire ready; wire [17:0] n_pow_5_implementation_1; wire [17:0] n_pow_5_implementation_2; wire [17:0] n_pow_5_implementation_3; initial begin clock = 1; forever # 50 clock = ! clock; end initial begin repeat (2) @(posedge clock); reset_n <= 0; repeat (2) @(posedge clock); reset_n <= 1; end pow_5_implementation_1 pow_5_implementation_1 (clock, reset_n, run, n, ready, n_pow_5_implementation_1); pow_5_implementation_2 pow_5_implementation_2 (clock, n, n_pow_5_implementation_2); pow_5_implementation_3 pow_5_implementation_3 (n, n_pow_5_implementation_3); integer i; initial begin $dumpvars; $monitor ("clock %b reset_n %b n %d comb %d seq %d run %b ready %b pipe %d", clock, reset_n, n, n_pow_5_implementation_1, n_pow_5_implementation_2, run, ready, n_pow_5_implementation_3); @(posedge reset_n); @(posedge clock); for (i = 0; i < 50; i = i + 1) begin n <= i & 7; run <= (i == 0 || ready); @(posedge clock); end $finish; end endmodule

An engineer simulated the testbench and got the following waveform. However he forgot the order he added the last three signals to the waveform. Can you determine which signal is the output of combinational implementation, sequential non-pipelined implementation and sequential pipelined implementation? a) The order is (from upper n_pow_5... to lower n_pow_5...): combinational, sequential non-pipelined implementation, pipelined b) combinational, pipelined, sequential non-pipelined implementation c) pipelined, combinational, sequential non-pipelined implementation d) pipelined, sequential non-pipelined implementation, combinational e) sequential non-pipelined implementation, combinational, pipelined f) sequential non-pipelined implementation, pipelined, combinational

Exam is created by Yuri Panchul with some code borrowing from Digital Design and Computer Architecture, Second Edition by David Harris and Sarah Harris, 2012